jdbakker

Well-known member

[quote author="Svart"]I guess I should explain what I am doing here, this circuit is gain for the output of a DDS(AD9911)(200mvP-P 50R loaded) to 2vP-P 50Rloaded into the REF port of a PLL, the AD4113. I found that during testing the difference between a 200mv(-10.5dbm) signal and a 2v(8dbm) signal is about 10dbm of phase noise at 10khz from the carrier.[/quote]

200mVpp is below the minimum ref input voltage for the ADF4113, so that's not too surprising. I have personally found those ADF parts to be more finicky than their LMX brethren, BTW.

So you don't really need any DC gain (or even point-one-dB predictable RF gain), as long as you can drive the REFIN hard enough without drooping off at higher frequencies, right? You also don't care much about linearity, IP3 and compression, as you're amplifying a (synthetic) sine wave and the first thing the signal hits inside your synth is a limiter anyway.

Solution #1: a step-up RF transformer, which could double as a balun. Something like the Mini-Circuits TC16-161T would do the job just fine.

#2: a monolithic microwave amp, like the ERA-6.

#3: a comparator, like the LT1720. Will add more jitter than #1 or #2, though.

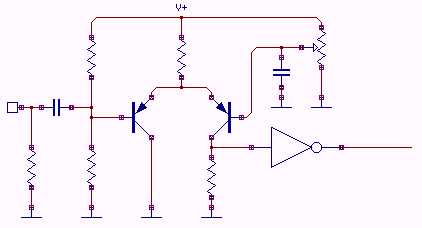

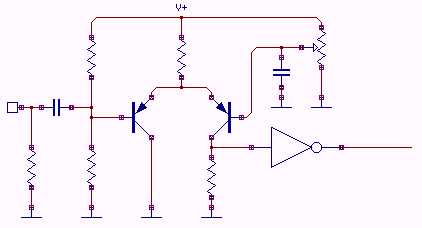

#4: Go discrete:

The inverter can be a single-gate LVC04. If you go an octave lower and add emitter degeneration you might even be able to use bog-standard 2N4403s; for higher frequencies I have had good luck with BFT92s in this configuration.

JDB.

200mVpp is below the minimum ref input voltage for the ADF4113, so that's not too surprising. I have personally found those ADF parts to be more finicky than their LMX brethren, BTW.

So you don't really need any DC gain (or even point-one-dB predictable RF gain), as long as you can drive the REFIN hard enough without drooping off at higher frequencies, right? You also don't care much about linearity, IP3 and compression, as you're amplifying a (synthetic) sine wave and the first thing the signal hits inside your synth is a limiter anyway.

Solution #1: a step-up RF transformer, which could double as a balun. Something like the Mini-Circuits TC16-161T would do the job just fine.

#2: a monolithic microwave amp, like the ERA-6.

#3: a comparator, like the LT1720. Will add more jitter than #1 or #2, though.

#4: Go discrete:

The inverter can be a single-gate LVC04. If you go an octave lower and add emitter degeneration you might even be able to use bog-standard 2N4403s; for higher frequencies I have had good luck with BFT92s in this configuration.

JDB.