Samuel Groner

Well-known member

Hi

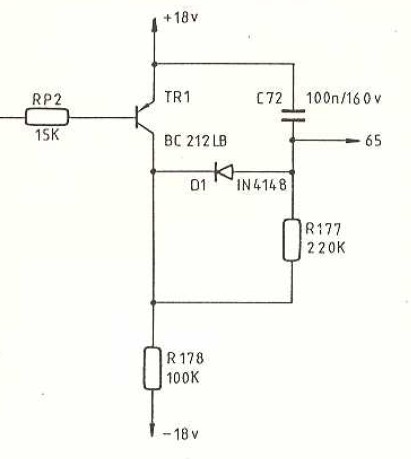

First time I use a FET switch so I have a few Qs. Application is a noise measurement amplifier, so distortion is not important but gain stability with temperature and age is. The current schematic:

The gain stage shown is preceded by a low-noise differential amplifier with 40 dB or 60 dB gain, switched by a 3-position rotary switch which switches the FET gates as well. The second stage as shown in the schematic provides gain calibration and additional 20 dB gain for an overall gain of 40 dB, 60 dB or 80 dB. Maximum level at the opamp's output is 14 Vpp.

And now the questions:

* Is the FET choice a good one? Just what I have ready with low Ron.

* How high shall I pull the gates for off? I have 3.3 V, 9 V and 18 V ready. Simulation indicates that 18 V shows best offness (although this is uncritical here), so I'd use this if there is no further drawback.

* As the gain switch of the first stage and the gate switching is mounted on the same switch, I'm somewhat concerned about capacitive coupling of these stages. How critical is this? Do I need to RC-filter close to the gates?

Thanks for your help!

Samuel

First time I use a FET switch so I have a few Qs. Application is a noise measurement amplifier, so distortion is not important but gain stability with temperature and age is. The current schematic:

The gain stage shown is preceded by a low-noise differential amplifier with 40 dB or 60 dB gain, switched by a 3-position rotary switch which switches the FET gates as well. The second stage as shown in the schematic provides gain calibration and additional 20 dB gain for an overall gain of 40 dB, 60 dB or 80 dB. Maximum level at the opamp's output is 14 Vpp.

And now the questions:

* Is the FET choice a good one? Just what I have ready with low Ron.

* How high shall I pull the gates for off? I have 3.3 V, 9 V and 18 V ready. Simulation indicates that 18 V shows best offness (although this is uncritical here), so I'd use this if there is no further drawback.

* As the gain switch of the first stage and the gate switching is mounted on the same switch, I'm somewhat concerned about capacitive coupling of these stages. How critical is this? Do I need to RC-filter close to the gates?

Thanks for your help!

Samuel