I'm also looking at the biasing of the FET in the U87 design. The drain resistor is 47K, which means that IDS cannot by definition be higher than about 0.5mA (assuming a VDD of 21.5V per the schematic).

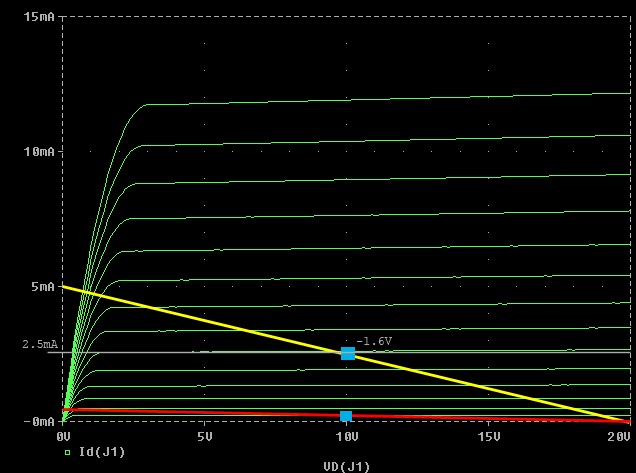

If you plot this load line on the 2N3819 (the red line below) you can see that the input voltage swing is pretty severely limited:

The simulation matches: signals beyond about 0.2V peak get clipped when the gate-source bias goes positive.

EDIT: this is wrong. It gets clipped when the transistor enters the linear region and drain current falls away.

I'm wondering about choosing a higher Q point for the FET, more up into the 2.5mA idle range (yellow load line on the plot). This would move the maximum input amplitude up above 0.5V peak before clipping, and even more important is the output impedance of the stage falls by almost factor of 10 (from 47K down to about 6K). I would guess that THD is much less as the slope of the VGS/IDS curve at this Q point is closest to a straight line.

I wonder why such a low idling point was originally chosen: was it a phantom power / current consideration? Pulling 2.5mA - 5mA doesn't stress out any phantom power supply (which is specified for 14mA into a dead short), I wonder what Neumann was thinking? Perhaps the capsules were capable of putting out much signal so the extra current doesn't buy better operation?