hifizen

Well-known member

Continued from "Another Bloak Hack..." thread in the drawing board section, now that the circuit is up and running on my workbench.

As mentioned, my idea was to start with tk's excellent BigFetBloak circuit, and modify it a bit for use in a hi-fi stereo. My goals were to provide for DC (or transformer) coupling with a servo if needed, headphone drive capability, and gains down to unity, while retaining the simple nature of the original as much as possible. A big thanks to bcarso, Samuel Groner and others who contributed design ideas in the drawing board thread. I think one of the best ideas to come out of that discussion was the diamond buffer for the output. There are still some minor details to sort out in the temperature compensation / servo and noise areas, but that will come later. For now, I'd like to present my results with the diamond buffer...

Here's the prototype, pretty much as built:

There are a few differences from the schematic as shown... I did not build the servo section, so R5 is more like 660 ohms (actually a trimpot for now, but trimmed to almost exactly the 660ohms LTSPICE predicted). I also substituted 2SC4793 / 2SA1837 transistors instead of BD139 / BD140 for the output (great specs, and about 50c each from Digikey). I used only a 1nF cap in the output Zobel, since I didn't have a 10nF film easily on hand, and I wanted to see how it would behave without as much Zobel damping.

The diamond buffer was tested open loop by grounding the +IN node, omitting the feedback network, and injecting signal directly at the Q6 base with a function generator.

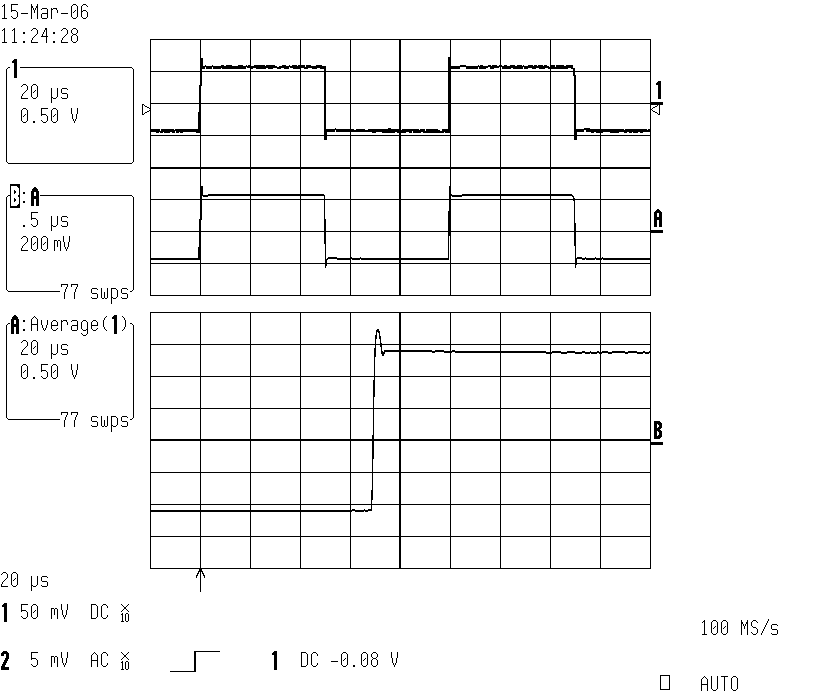

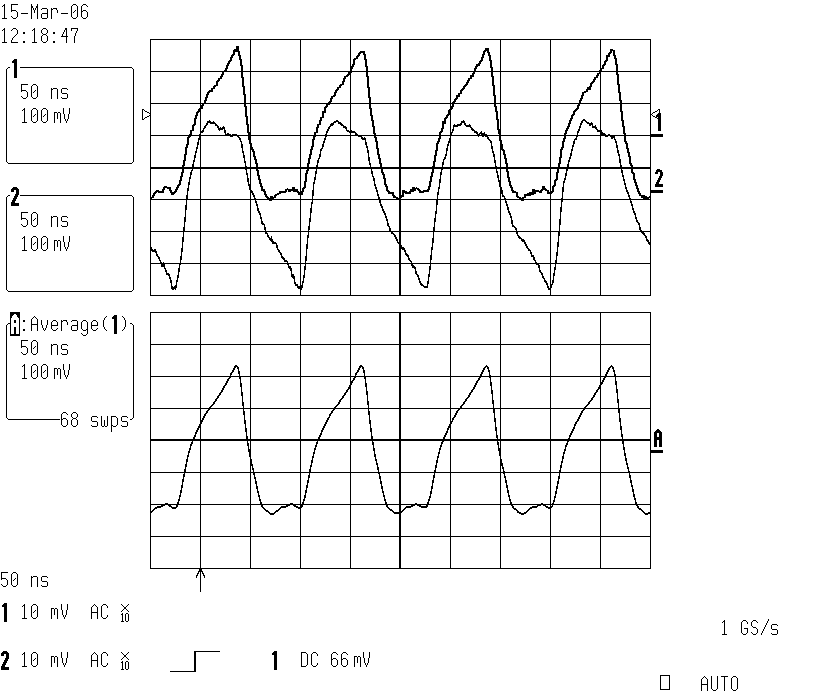

100kHz square wave response looked promising:

But as I mentioned in the old thread, sine wave response collapses into a distorted triangle wave at about 7MHz. Trace 2 shows the input waveform measured at Q6 base:

The input signal is only mildly distorted as this is happening - it still basically looks like a decent sine wave. In order for the stage to recover, the frequency has to back off all the way down past about 4MHz. I'm not entirely sure why this frequency hysteresis effect exists.

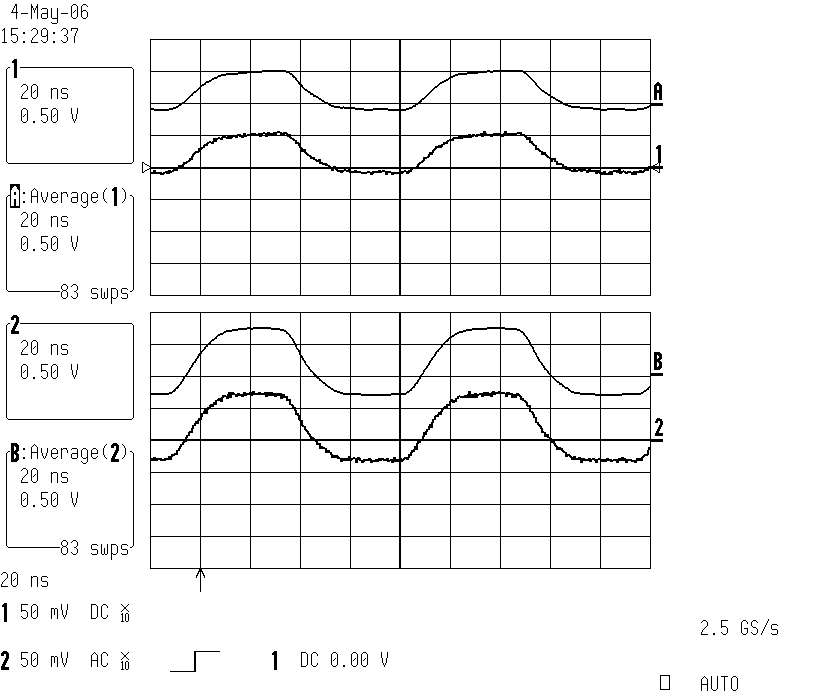

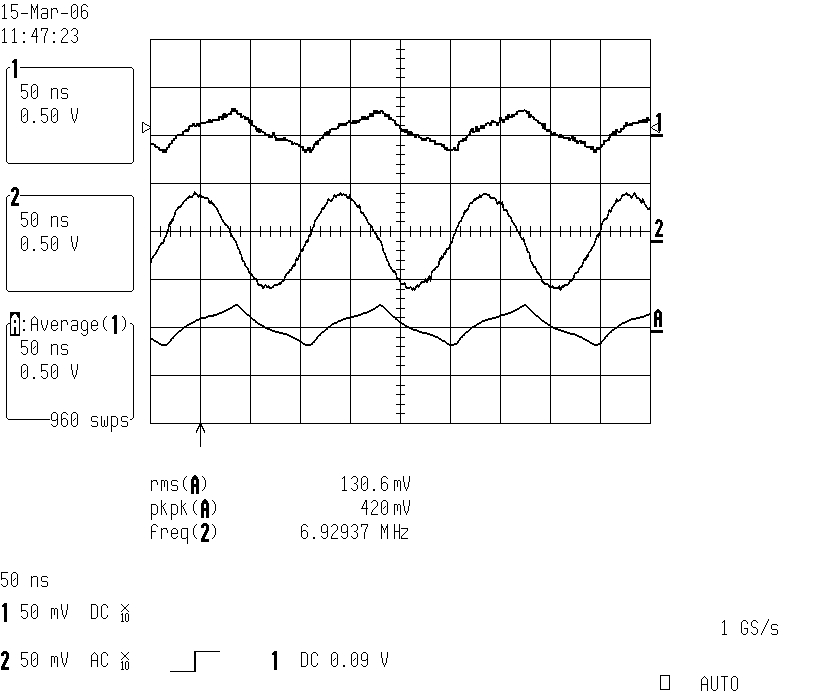

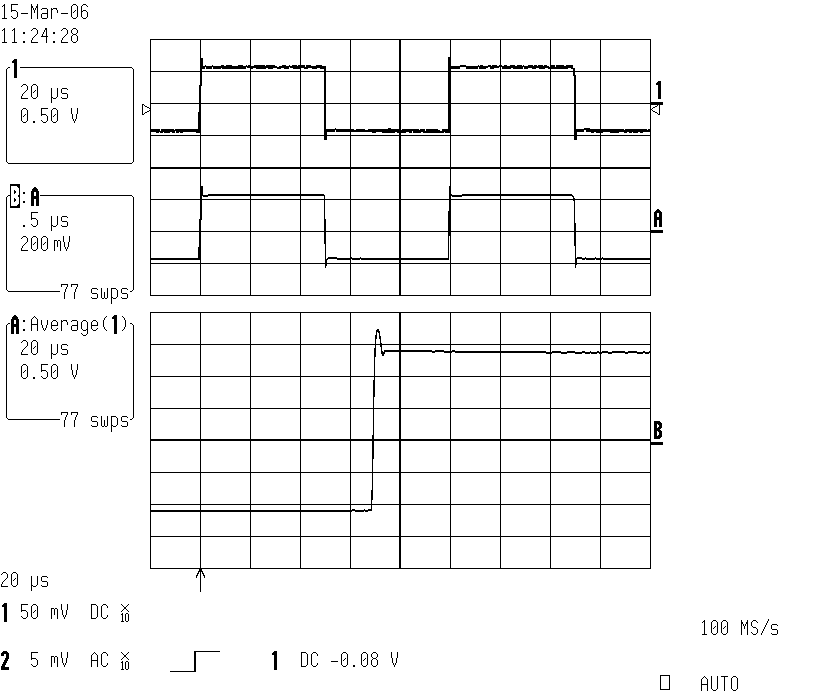

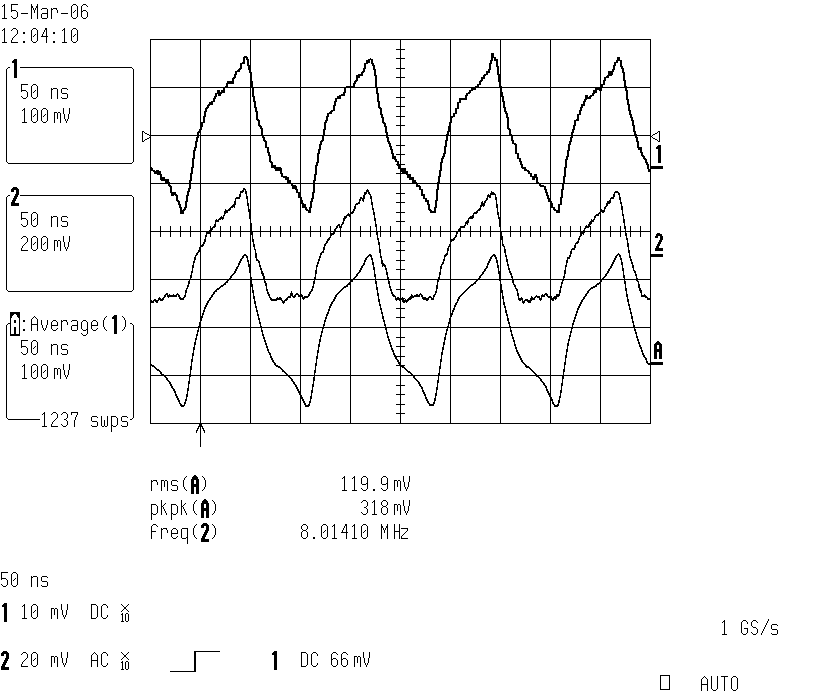

For a better look at what's going on, I measured waveforms at Q6 and Q7 emitters. This capture shows the output waveform at 8MHz (trace 1, averaged version at A), and the Q6 emitter waveform (trace 2"):

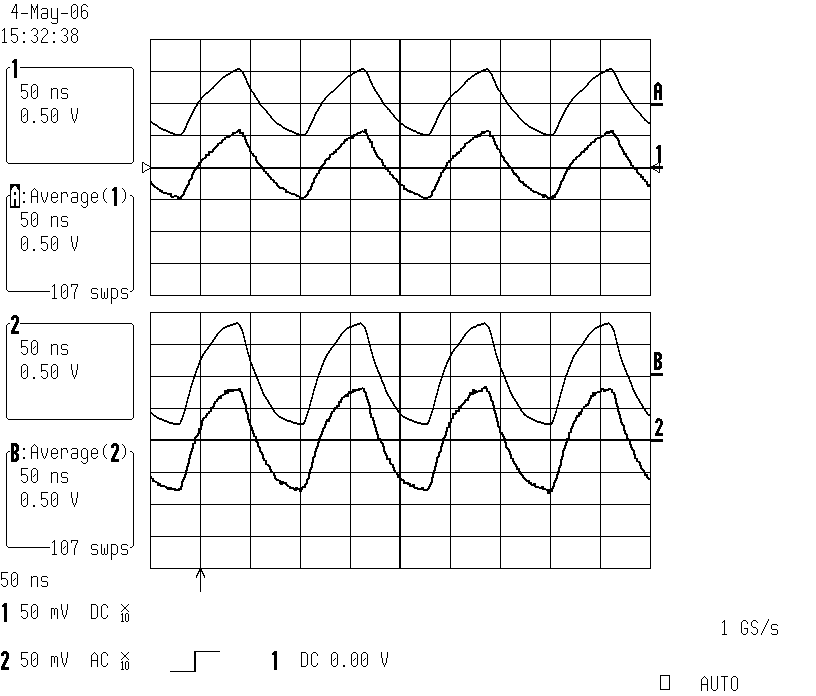

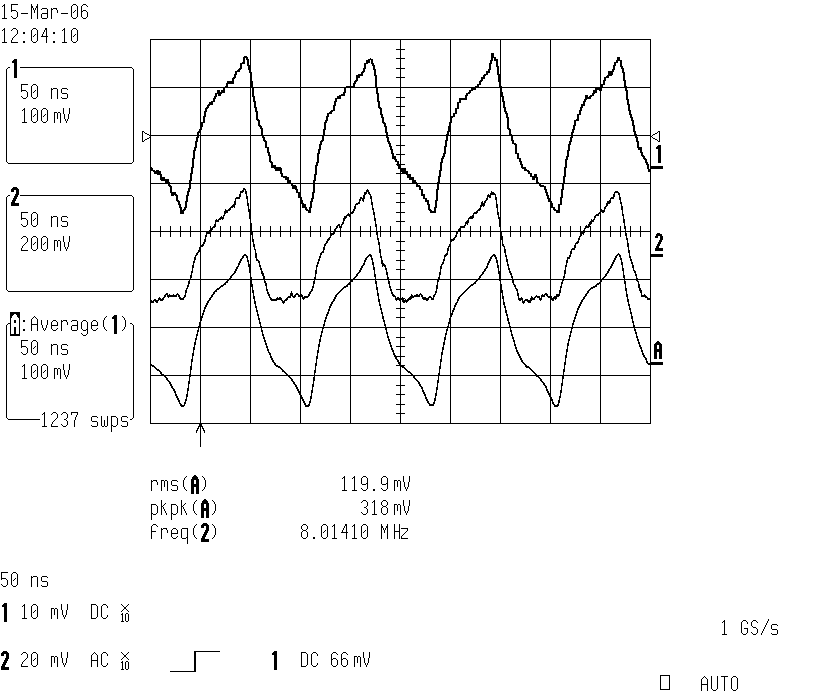

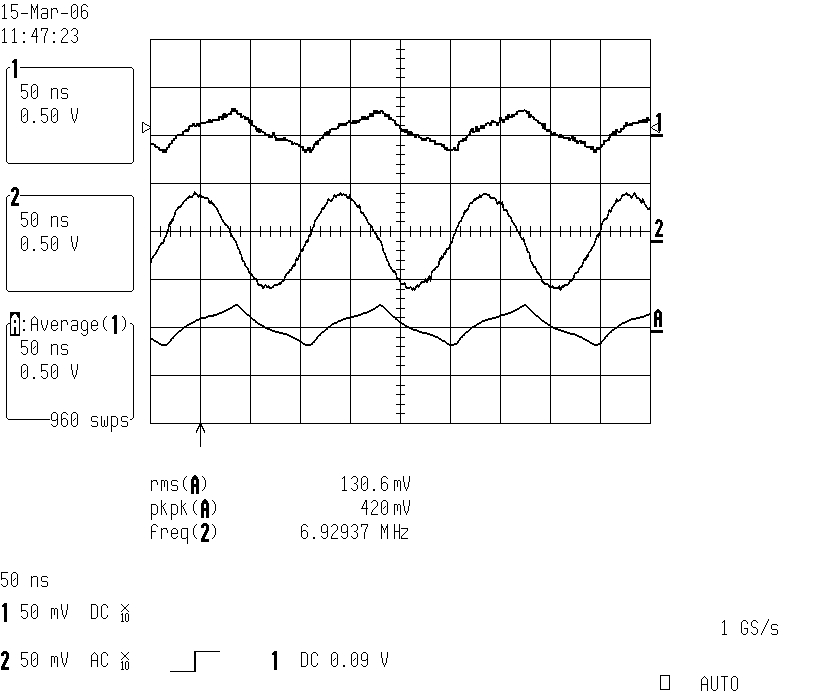

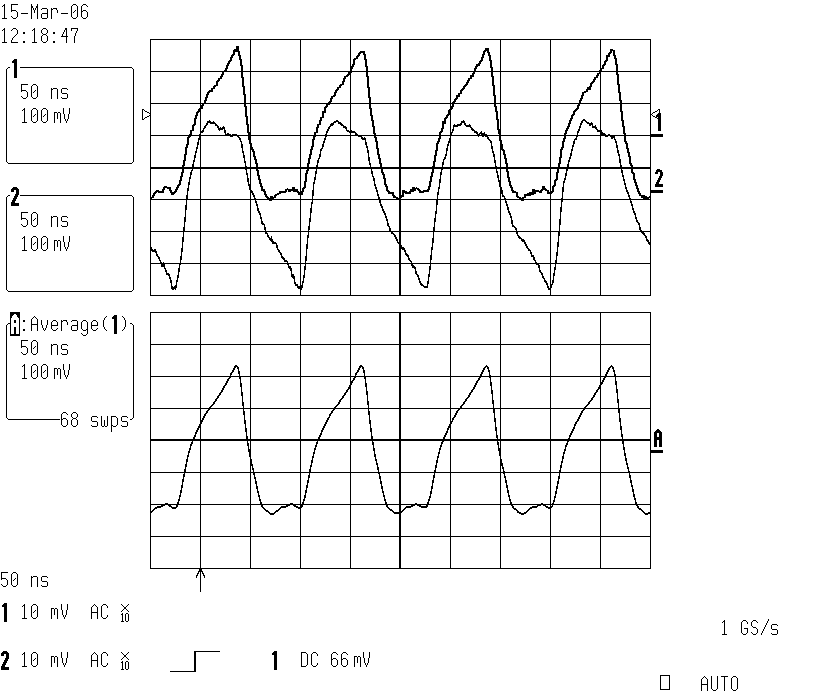

and this one shows Q6 and Q7 emitter waveforms at the same time:

My thought right now is that Q6 and Q7 are not running at a high enough standing current, and are running out of steam at high speed. Due to the loading problem presented by the bootstrap arrangement, I've decided to try switching to FET current sources instead to see how that does. I'll start off at about 6mA for each driver, and increase from there if necessary.

Any further insight into what's going on with those waveforms would be most welcome.

As mentioned, my idea was to start with tk's excellent BigFetBloak circuit, and modify it a bit for use in a hi-fi stereo. My goals were to provide for DC (or transformer) coupling with a servo if needed, headphone drive capability, and gains down to unity, while retaining the simple nature of the original as much as possible. A big thanks to bcarso, Samuel Groner and others who contributed design ideas in the drawing board thread. I think one of the best ideas to come out of that discussion was the diamond buffer for the output. There are still some minor details to sort out in the temperature compensation / servo and noise areas, but that will come later. For now, I'd like to present my results with the diamond buffer...

Here's the prototype, pretty much as built:

There are a few differences from the schematic as shown... I did not build the servo section, so R5 is more like 660 ohms (actually a trimpot for now, but trimmed to almost exactly the 660ohms LTSPICE predicted). I also substituted 2SC4793 / 2SA1837 transistors instead of BD139 / BD140 for the output (great specs, and about 50c each from Digikey). I used only a 1nF cap in the output Zobel, since I didn't have a 10nF film easily on hand, and I wanted to see how it would behave without as much Zobel damping.

The diamond buffer was tested open loop by grounding the +IN node, omitting the feedback network, and injecting signal directly at the Q6 base with a function generator.

100kHz square wave response looked promising:

But as I mentioned in the old thread, sine wave response collapses into a distorted triangle wave at about 7MHz. Trace 2 shows the input waveform measured at Q6 base:

The input signal is only mildly distorted as this is happening - it still basically looks like a decent sine wave. In order for the stage to recover, the frequency has to back off all the way down past about 4MHz. I'm not entirely sure why this frequency hysteresis effect exists.

For a better look at what's going on, I measured waveforms at Q6 and Q7 emitters. This capture shows the output waveform at 8MHz (trace 1, averaged version at A), and the Q6 emitter waveform (trace 2"):

and this one shows Q6 and Q7 emitter waveforms at the same time:

My thought right now is that Q6 and Q7 are not running at a high enough standing current, and are running out of steam at high speed. Due to the loading problem presented by the bootstrap arrangement, I've decided to try switching to FET current sources instead to see how that does. I'll start off at about 6mA for each driver, and increase from there if necessary.

Any further insight into what's going on with those waveforms would be most welcome.