Ok, this is a quick and not particularly well optimised try at what I would probably do.

How it works (and some discussion of compromises):

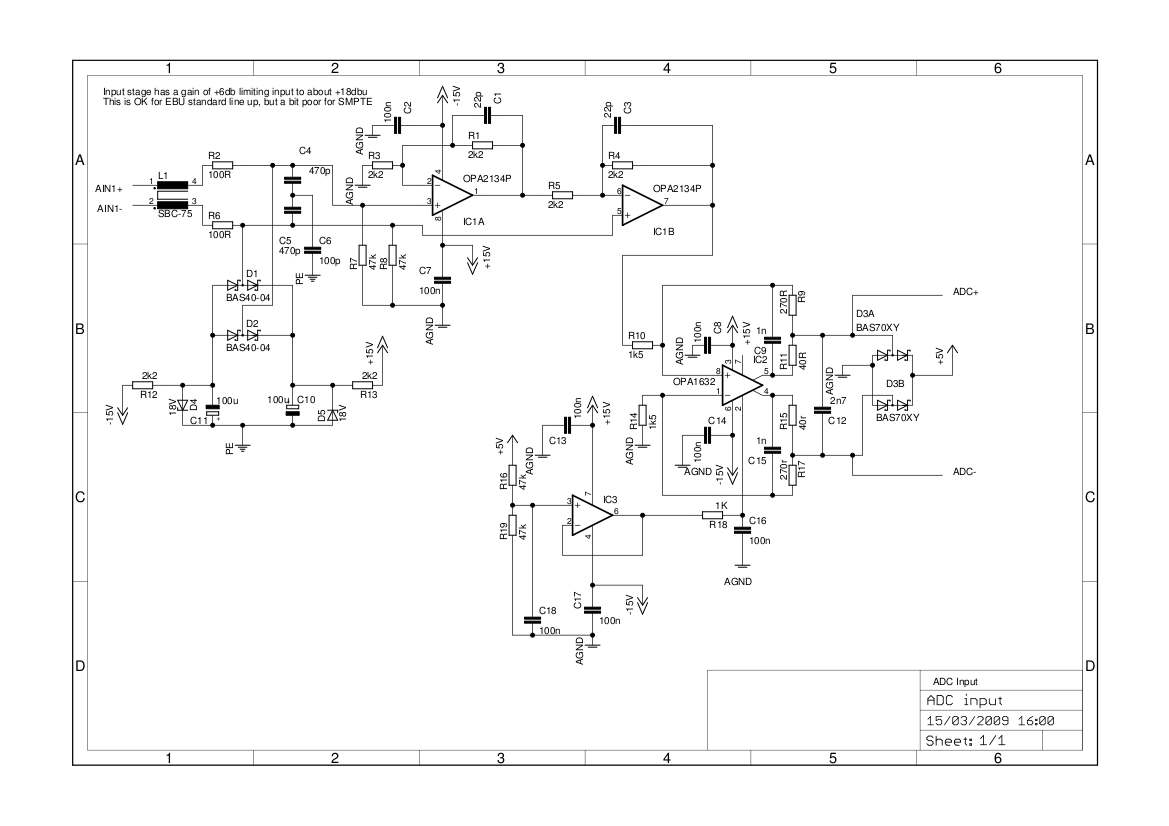

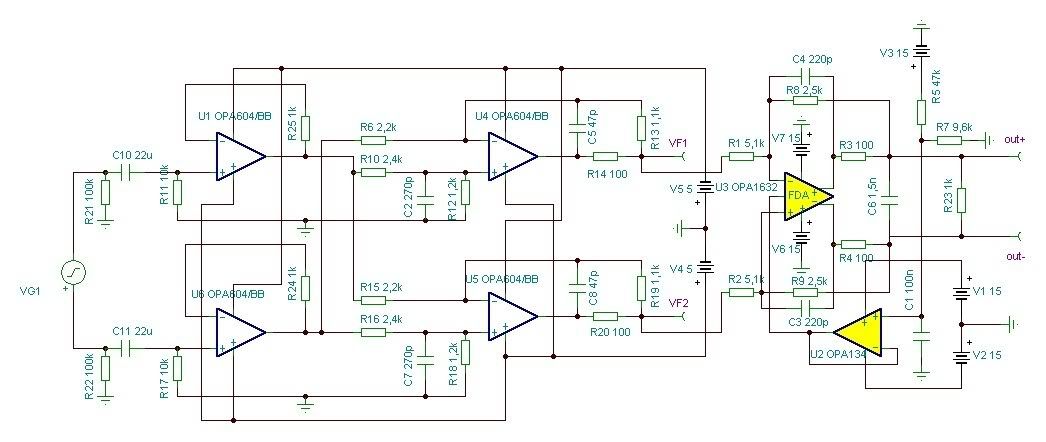

After my normal common mode choke, the input hits an input protection network R2 R6, D1, D2 and associated parts. R2 and R6 serve to limit transient currents but must be kept fairly small to avoid unbalance here spoiling CMRR and to avoid their thermal noise contribution degrading SNR unnecessarily.

The capacitive filter to remove RF around C4 C5 & C6 is set up to minimise the damage to CMRR and common mode impedance due to cap tolerance, common mode will be dominated by C6 which will reduce the effect of tolerances in C4,5 converting common mode to differential mode.

Note that PE should be a low impedance connection to the case and should not be a mile long connection back to the star point, get it close to the input connector.

As a high input impedance was part of the design brief, I punted for a superbal stage which can have almost arbitrarily high input impedance (Set by R7 and R8 here), note that the noise floor will probably be dominated by these when the input is O/C. The single opamp approach suffers badly when you make the resistors large as the resistor thermal noise is unavoidably in series with the input, so the extra opamp was worth it in my view.

R1,3,4 & 5 need to be matched for good CMRR, these could probably be made a little smaller to improve noise performance at the cost of loading the opamps more heavily, but 2K2 feels like a reasonable sort of compromise. This input stage suffers from always having a gain of 6db, which would be a problem is trying for an input stage suitable for the SMPTE alignment of +4dbu = -20dbFS (implies full scale at +24dbu) as the opamps would run out of headroom and clip.

The output of this stage is then fed single ended to the 1632 stage, which is biased to 2.5V by IC3 and associated components. With +2.5V bias there will be a standing current of a little over a mA flowing in the input resistors which should not be a problem.

Note that all this is DC coupled, mostly because I could not find a good place for a blocking capacitor (A general issue with low Z audio circuits, you need big ones), 10uf in series with each input would be possible, it depends on the application.

The 1n caps (C9,15) at the output form a low pass filter in combination with the feedback resistors (R9,17) which is -3db at about 500Hkz. These caps are required for opamp stability anyway, I just made them larger then would otherwise be required.

Go ahead and shred it!

Regards, Dan.

![Soldering Iron Kit, 120W LED Digital Advanced Solder Iron Soldering Gun kit, 110V Welding Tools, Smart Temperature Control [356℉-932℉], Extra 5pcs Tips, Auto Sleep, Temp Calibration, Orange](https://m.media-amazon.com/images/I/51sFKu9SdeL._SL500_.jpg)