Samuel Groner

Well-known member

Yes perhaps the limits are a bit optimistic. As long as the errors are monotonic (i.e. do not jump e.g. with range switching) it should be possible to find suitable RC corrections; but there are errors which definitely are not monotonic, the one from DC offset I mentioned is an example. But as long as I don't have a precision meter at 300 kHz there is anyway not much to be done about flatness.

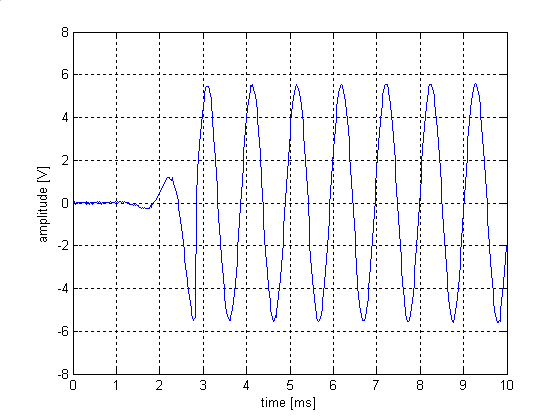

In any case next step is to derive a promising peak hold/sample-and-hold combo and test it. I'm also waiting for a discrete multiplier board to arrive which should replace the opto resistors (for the amplitude/Q control).

Samuel

In any case next step is to derive a promising peak hold/sample-and-hold combo and test it. I'm also waiting for a discrete multiplier board to arrive which should replace the opto resistors (for the amplitude/Q control).

Samuel